https://www.youtube.com/watch?v=ooGHcZFvfVQ

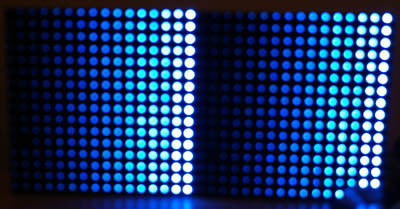

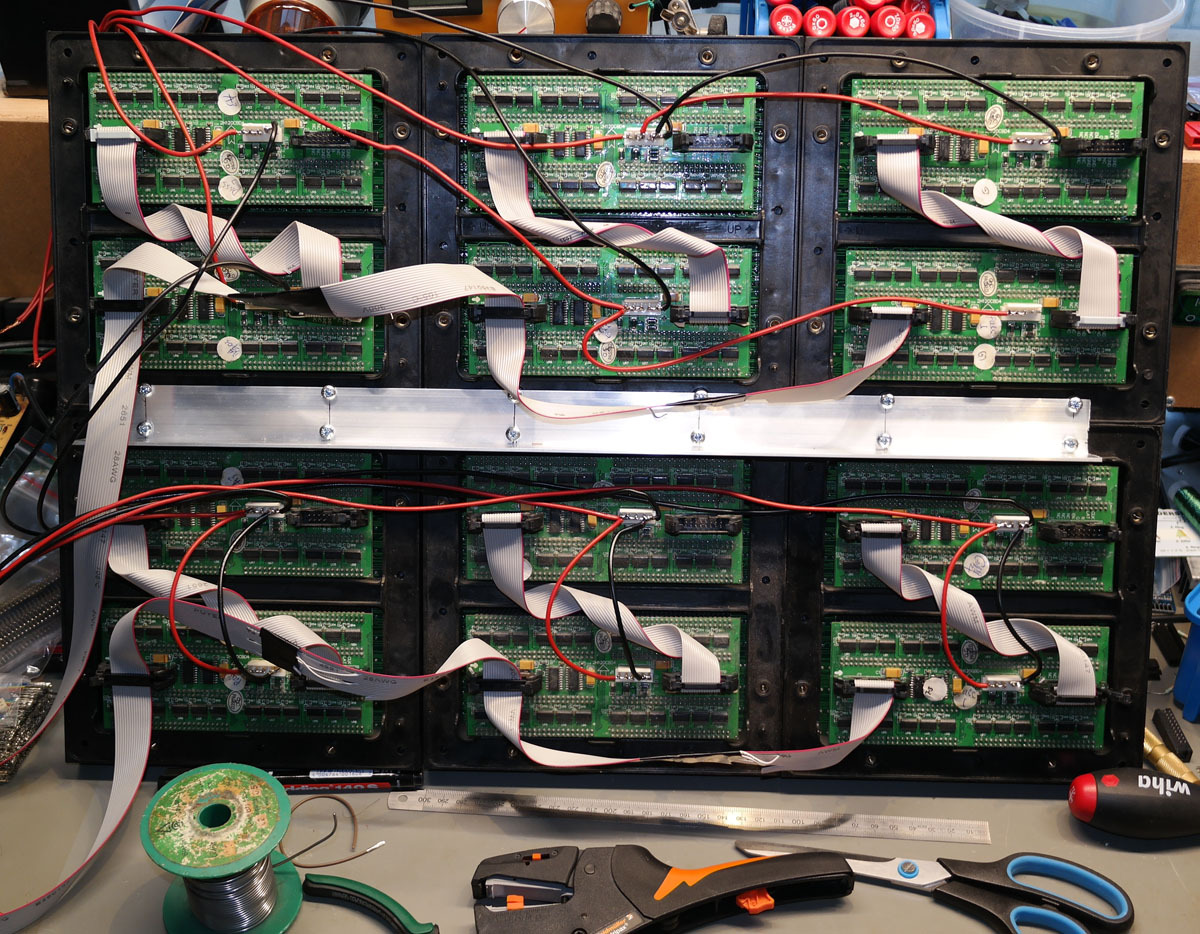

Noch mit Debug-Pixel (unterste ist FrameSize, oberne ist FrameZähler)

Helligkeit : Dank Bitangle_Modulation erreicht es nur noch ca 60% Tastgrad, dazu ist es mit PWM über Widerstand & Diode gemischt, (10/255 PWM)

Rechnet ruhig selber aus

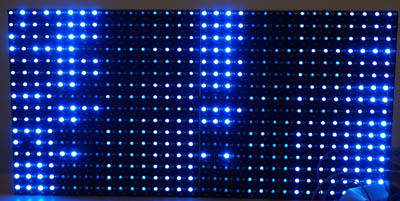

Mometan hab ich eher seltene Übertragungsfehler (der zum erlischte Bild führt) Dank Debug-Pixel kann ich sehen, dass FrameSize-Übertragung gescheitert ist. (auf 0 gesprungen, soll 512 sein)

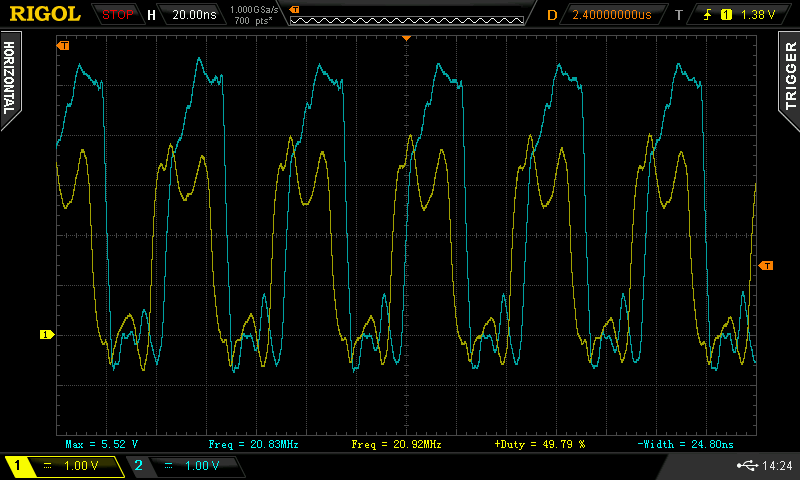

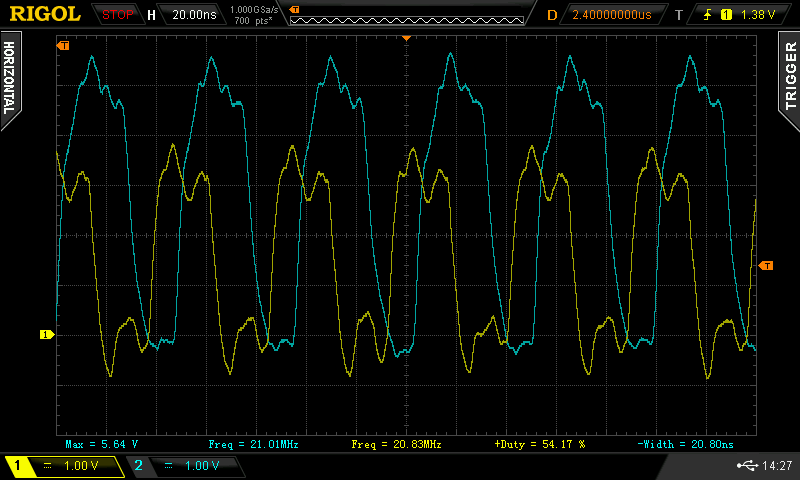

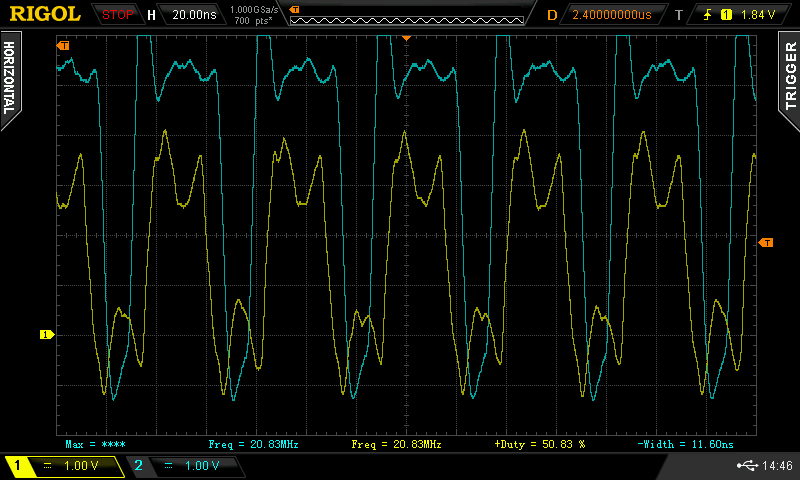

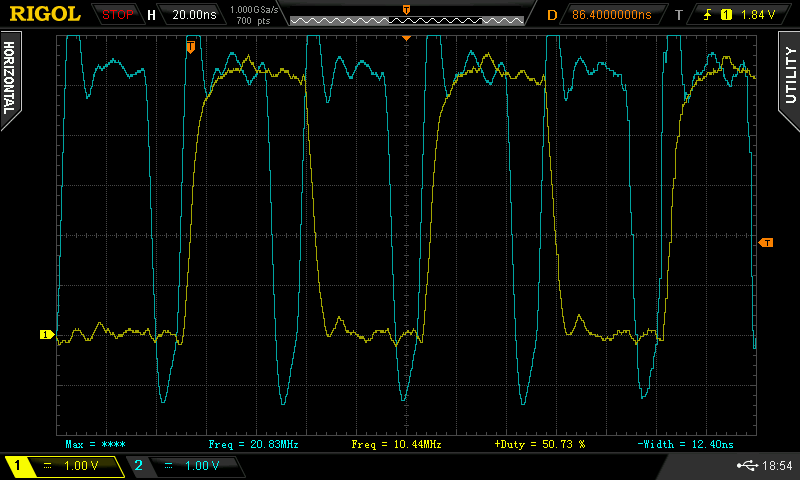

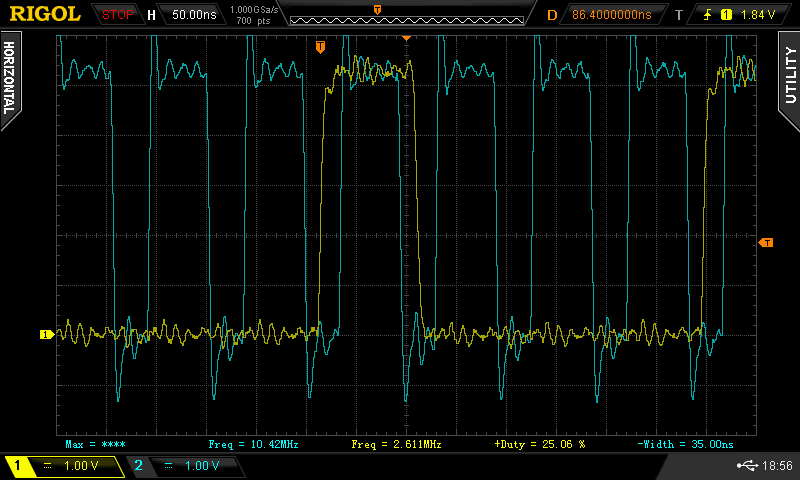

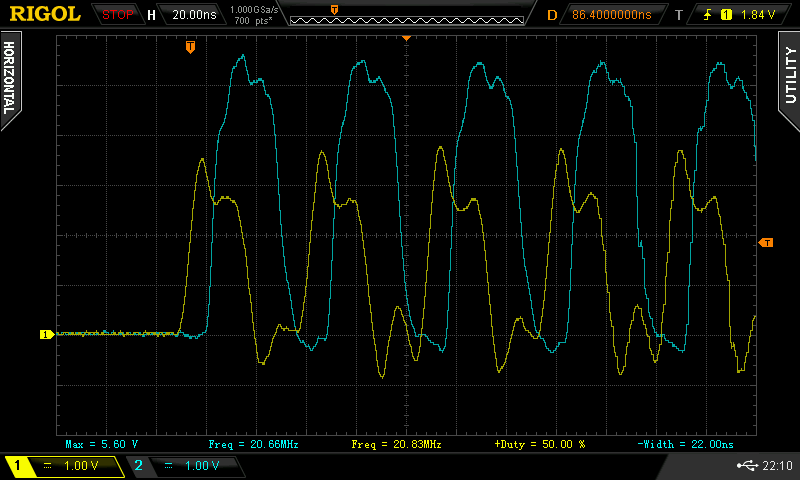

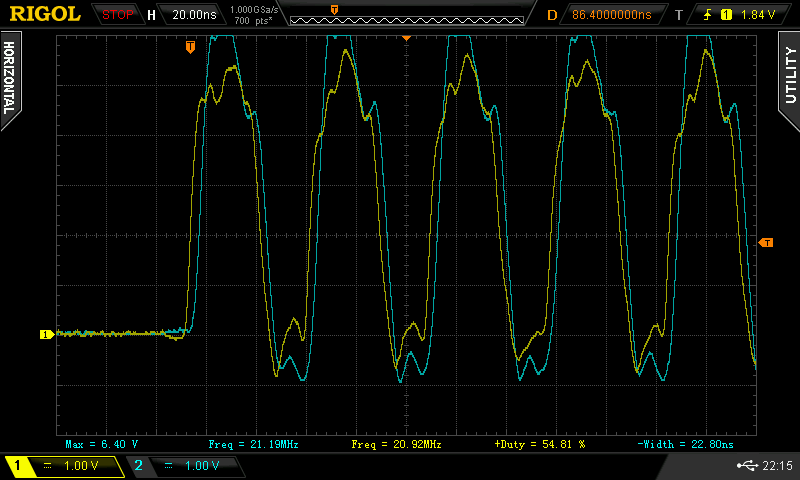

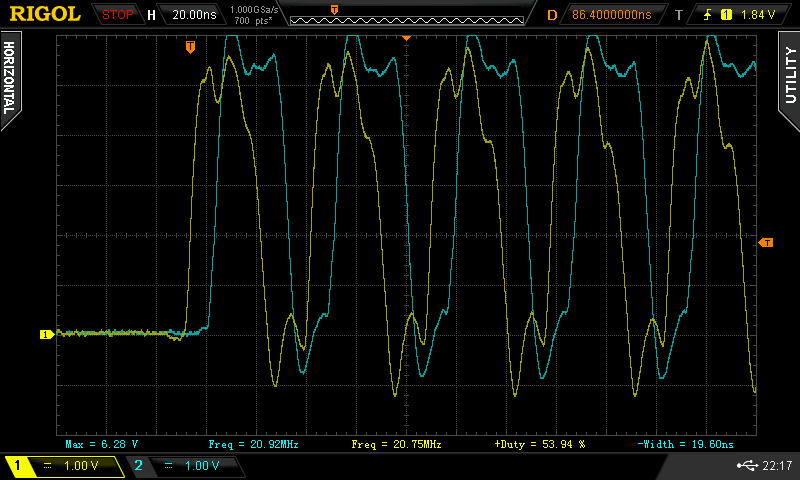

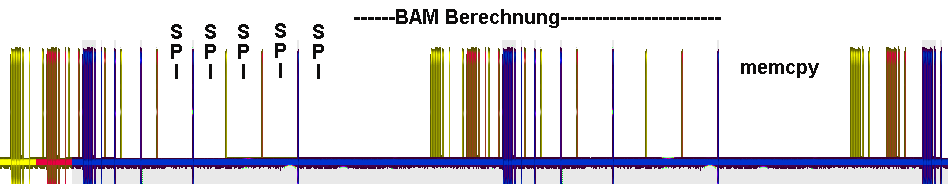

So sieht UART-Übertragung und ihre UART-Auslesroutine aus.

Man sieht viel Lücke, da AVR wesentlich schneller mit auslesen ist und bricht Auslesroutine ab, wenn der "kein Daten in Ringbuffer" -Flag erkennt.

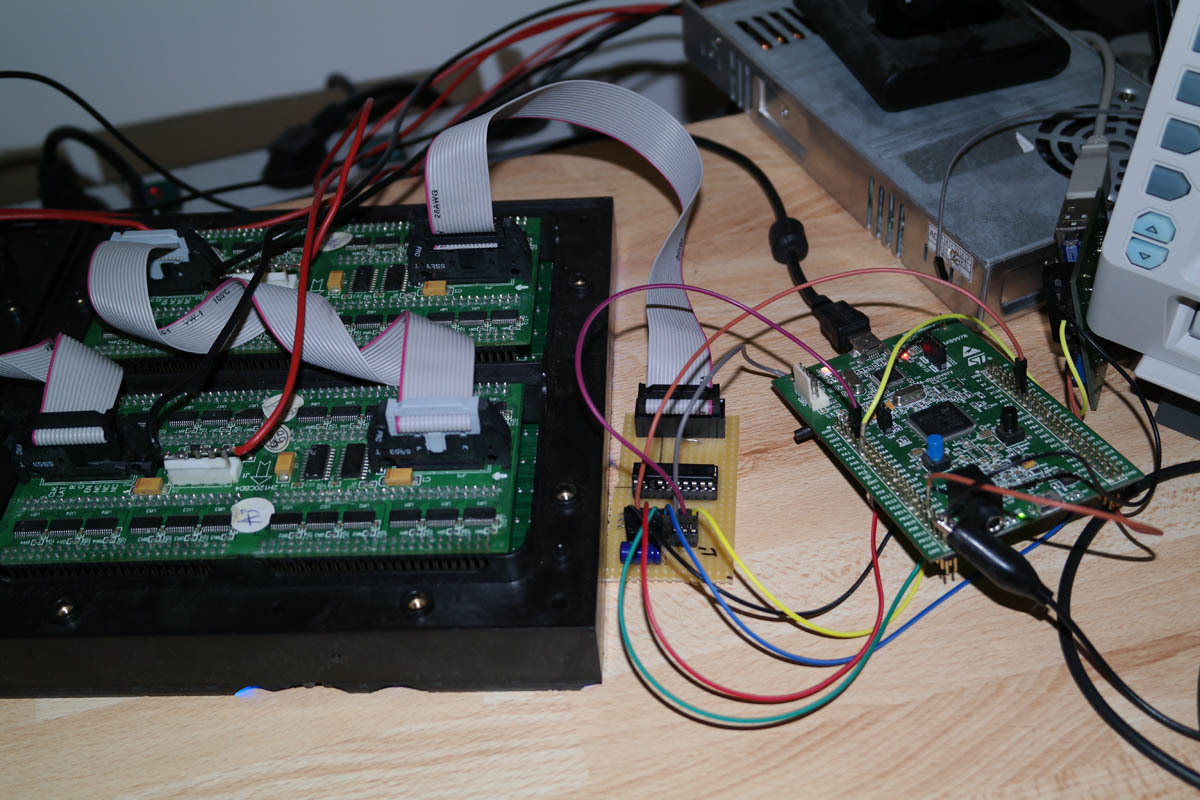

Alls wird bis auf FrameCount (TPM2-Byte-Framezähler) und eine(Soft-) Register zurückgesetzt.

Bei nächste Ausles-Zyklus wird der anhand Register prüfen. Register steuert dann diese Zyklus , ob der auf Startbyte prüfen soll ,weiter Framebuffer füllen sollen oder auf Stop-Byte prüfen und ggf. alles zurücksetzen.

Zyklische Abbrechen (durch "kein Daten in UART RIngbuffer") von Auslesroutine ist gewollt, sonst geht FPS massiv in Keller und es flackert.

Man sieht gut dass Lücke 2 verschiedene Breite hat. Das kommt von Bitangle-Modulation