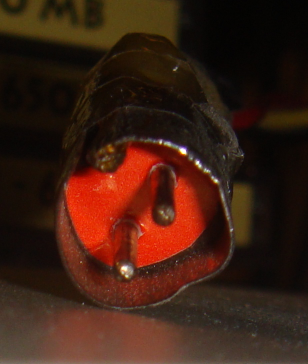

Das Wunder chinesischer KInderhände oder wie schafft man sonst noch Schrumpfschlauch um die Kontakte eines so einen dicht besetzten Stecker zu packen?

ferdimh hat geschrieben: ↑Mi 15. Jan 2020, 23:39

Es stellt sich die Frage, ob man das RAM-Interface noch als "parallel" bezeichnen kann. Bei aktuellen Taktungen liegt bereits de facto ein serielles Interface vor. Bei DDR3/4 werden schon pro Taktschwingung 8 Bits übertragen... - bei DDR4 macht ein einzelner Pin schon mehrere GBit/s.

Die Pinanzahl ergibt sich bei bereits weit im GHz-Bereich liegenden Interfacetakten auch durch die Notwendigkeit, derartig extreme Datenmengen durchzupumpen. Bei "normalen" Steckerbauformen und Leiterbahnen ist halt bei einstelligen GHz Schluß.

Es ist immernoch DDR, also 2 Bits/Takt/Pin.

Bei DDR4 zB gibts nicht mehr nur Banks im DRAM IC, sondern auch Bank Groups, also quasi 16 Bänke.

Ansonsten steigt "nur" immer mehr der Takt des Interface zwischen CPU und DRAM.

Innerhalb des DRAM nimmt die Bitbreite immermehr zu, denn der DRAM an sich wird nicht wirklich schneller.

Also was in 1 Takt aus dem DRAM ausgelesen wird (sehr breit) wird dann in vielen Takten übers schmale Interface übertragen.

Pro DDR4 DRAM IC werden intern 64Bit ausgelesen und dann über 8Bit ausgegeben, aber DDR.

(ist eben wieder die Frage was man hier als seriell bezeichnet, das Interface ist es nicht)

sub hat geschrieben: ↑Mi 15. Jan 2020, 10:57

TRX40 hat ja Drehmomentschraubendreher dabei

Ja das macht AMD löblich.

Bei INtel musste erstmal die CPU am Kühler montieren und dann auf den Sockel legen und dann festziehen.

Ein DRAM Kanal zickt dann manchmal, also wiederholen.

b0n3 hat geschrieben: ↑Mo 13. Jan 2020, 23:54

Alternativ zu Pins könnte man ja auch die coolen Goldschwämme verwenden die IBM in ihren Mainframes verwendet

(Igor!! mehr Anpressdruck!!!)

Ja, hab ich "letztens" beim Play With Junk Schweizer gesehen, der Hammer!

@Sir_Death

Erzähl deinen Kollegen doch mal was von dem 64Kerner mit die was zu sabbern haben )