Eine Regenbogentabelle hab ich nicht, nein.

Es geht auch nicht darum in 2 Takten oder so zu dividieren.

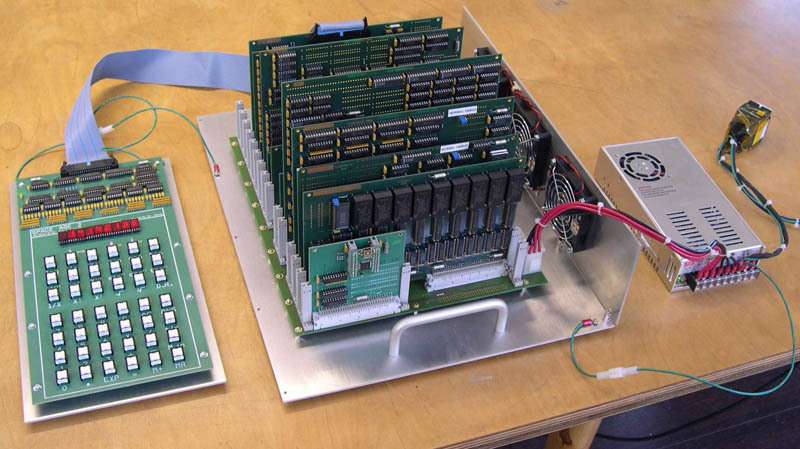

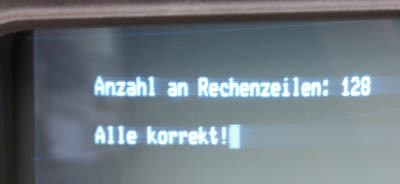

Multiplikationen: genau 67 Takte

Divisionen so 100 Takte.

Nach 100 Takten war die Emulationsroutine noch nichtmal mitm Register sichern aufn Stack fertig

So sehr beschleunigt die MulDiv Karte.

Dividieren ist Multiplizieren rückwärts.

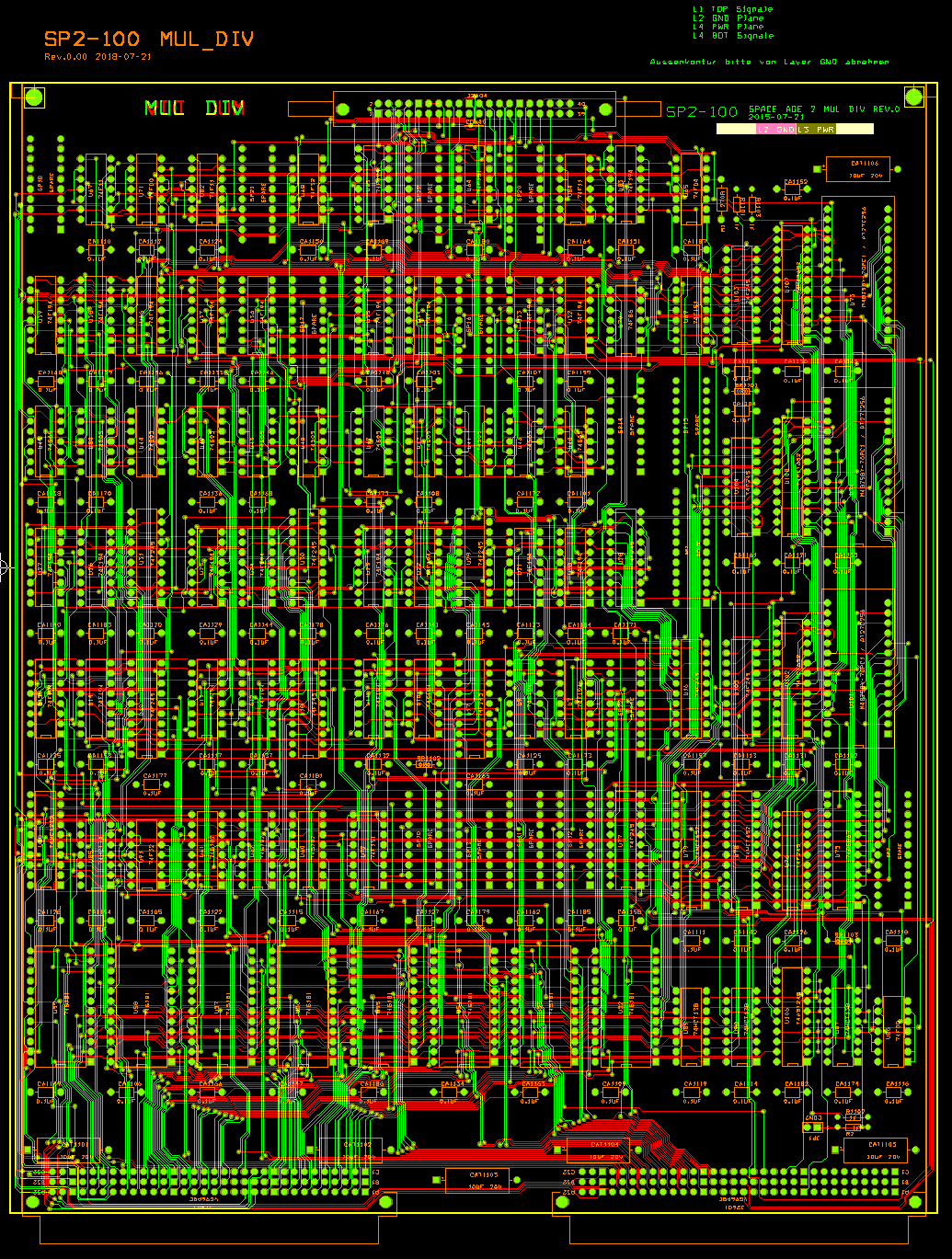

(serielles Multiplizieren und Dividieren)

Dazu erstmal ne Erklärung des vorzeichenlosen Multiplizieren:

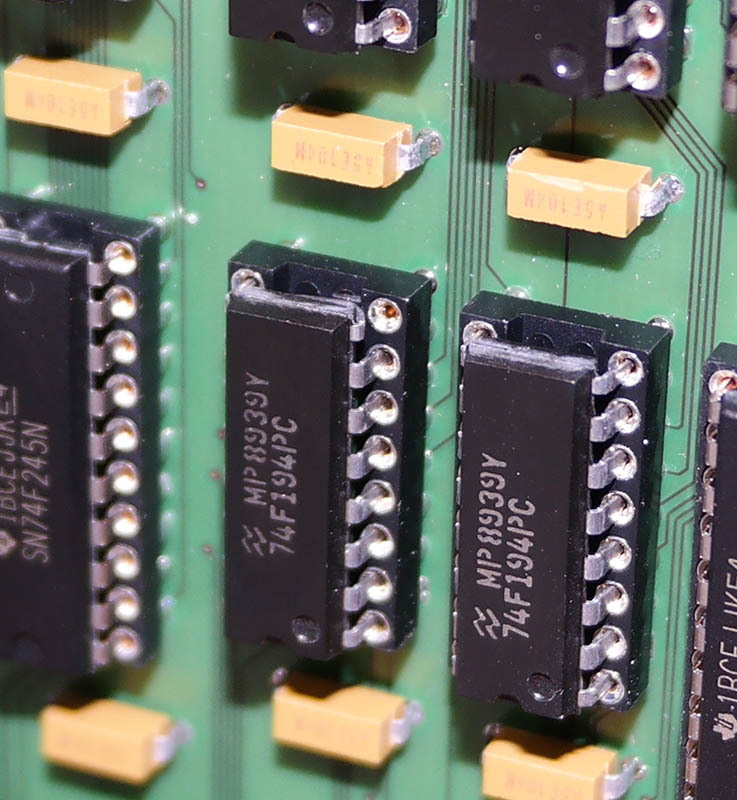

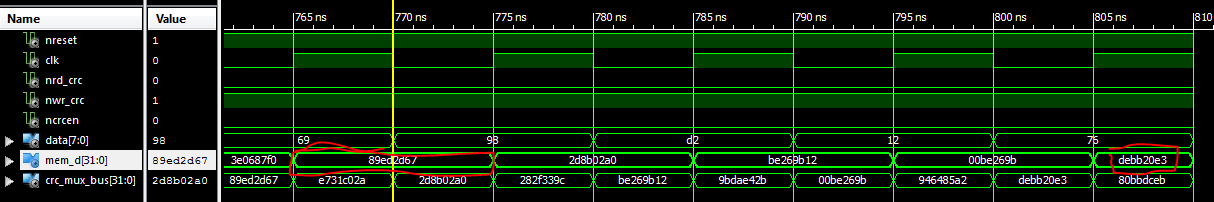

Es existieren 2 32 Bit Schieberegister, HI und LO.

In LO wird der eine Multiplikant reingeschrieben, der zweite Multiplikant liegt dauerhaft auf dem Bus an, der zur ALU geht.

Das HI Register muss genullt werden.

Jetzt werden HI Register und der Multiplikant auf dem Bus miteinander addiert.

WENN das Bit0 des LO Registers 1 ist, dann wird die Summe nach HI geschrieben.

WENN das Bit0 des LO Registers 0 ist, dann wird die Summe nicht geschrieben.

Jetzt werden HI und LO nach rechts geschoben, wobei das aus HI "rausfallende" Bit nach LO reingeschoben wird.

Es wird also Stück für Stück das Ergebnis nach LO geschoben, welches dann auch die unteren 32Bit des Ergebnisses enthält.

Durch das Schieben ist Bit0 des LO Registers wieder ein anderes und das Ganze macht man dann 32 mal.

Addieren und schieben sind jeweils ein Takt -> 64 Takte, dazu noch etwas Übergabegedöhns von der CPU zur MulDiv Karte -> 67 Takte.

Im Endeffekt ist das wie die schriftliche Multiplikation in der Grundschule, nur eben Binär.

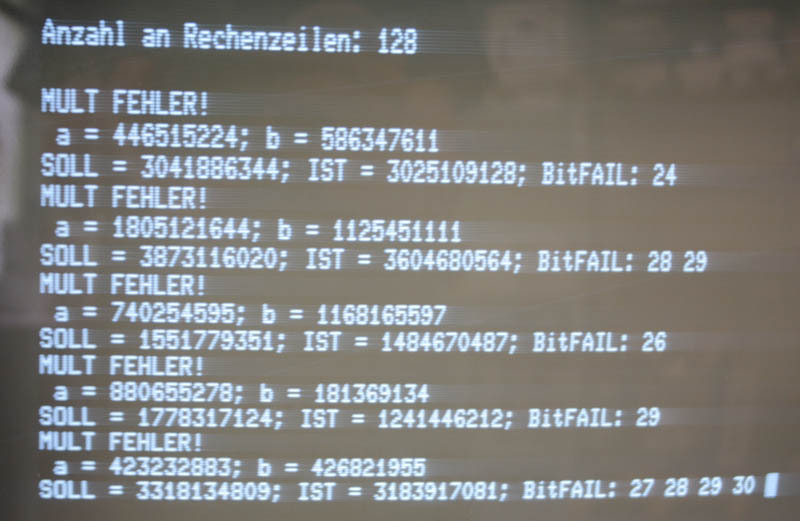

Beim Dividieren ohne Vorzeichen:

Wie war das mit dem Rückwärts?

Es wird zuerst geschoben und dann auchnoch nach links!

Addieren? Nö, Subtrahieren.

Genauer:

Zuerst HI nach links schieben (welches sich dann das neue Bit0 aus dem LO zieht).

Dann HI = HI - Divisor, der auf dem Bus liegt.

Wenn der Borrow Ausgang des Subtrahierers nicht gesetzt ist (also das Ergebnis passt noch), dann wird das Ergebnis in HI gespeichert.

Wenn das Borrow gesetzt wird, dann nicht. Das Ergebnis muss quasi noch in HI "passen", also darf nicht negativ werden.

Beim LO shiften nach links wird das Borrow auch wieder ausgewertet:

Borrow = 0 -> es wird eine 1 reingeschoben, sonst 0.

Das LO Register merkt sich also wann er Subtrahieren konnte ohne, dass es negativ wurde und das ist dann auch schon das Ergebnis.

Was am ende im HI übrig bleibt ist wortwörtlich der Rest.

Vorschrift in C für 4 Bit:

(Ich hab ja die Algorithmen zuerst in C Bitschubserei getestet)

Code: Alles auswählen

void perform_ud(uint32_t* rem, uint32_t* quot, uint32_t uopA, uint32_t uopB){

//init right half of shift with quotient

uint8_t shiftregister = uopA;

shiftregister &= 0x0F;

uint16_t alu_erg = 0;

unsigned i;

for (i = 0; i < 4; i++){

//left shift

shiftregister <<= 1;

shiftregister &= 0xFE;

alu_erg = (shiftregister >> 4) - (uint8_t)uopB;

//if alu_erg is negative (bit n-1 is 1) -> dont save and shiftregister lsb = 0

//if alu_erg is positive (bit n-1 is 0) -> save and shiftregister lsb = 1

if((alu_erg & 0x100) == 0x100){ //borrow abfragen!

//if((shiftregister >> 4) < uopB){

;

}else{

alu_erg &= 0xFF;

shiftregister &= 0xF;

shiftregister |= (alu_erg << 4) | 1;

//printf("write q0 at %i\n", i);

}

}

*rem = (shiftregister >> 4);

*quot = shiftregister & 0x0F;

}